# DISPOSITIVOS LÓGICOS PROGRAMABLES (PLD)

#### PLD

- Obspositivo lógico programable:

- Circuito prefabricado que incluyen dos capas de interconexión flexibles.

Equivalen a miles de compuertas lógicas.

- Expresiones de conmutación básicas de dos niveles

#### PLD

- Integran fácilmente aplicaciones y desarrollos lógicos.

- Empaquetamiento en un circuito integrado

- Reducen espacio físico

- ASIC (Circuitos integrados de aplicación específica) → Se sustituyen por FPGA y CPLD

#### **C**ATEGORÍAS

- Diseño totalmente a la medida (Full-Custom)

- Libertad total de diseño, requiere todas las etapas de fabricación.

- Riesgos y costos muy elevados. (Alta prod.)

- Matrices de compuertas predifundidas (Semi custom/gate array)

- Estructura regular de dispositivos básicos, prefabricada, personalizable.

- Diseño limitado a la estructura prefabricada.

#### **C**ATEGORÍAS

- Celdas estándar precaracterizadas (Semi custom/standard cells)

- Sin estructura prefabricada, tiene bibliotecas de celdas y módulos precaracterizados.

- Libertad de diseño (facilidades de la biblioteca), requiere diseños completos

- Lógica programable (CPLD, FPGA)

- Dispositivos fabricados personalizables mediante programación.

- Basada en bibliotecas y mecanismos específicos programables por Software

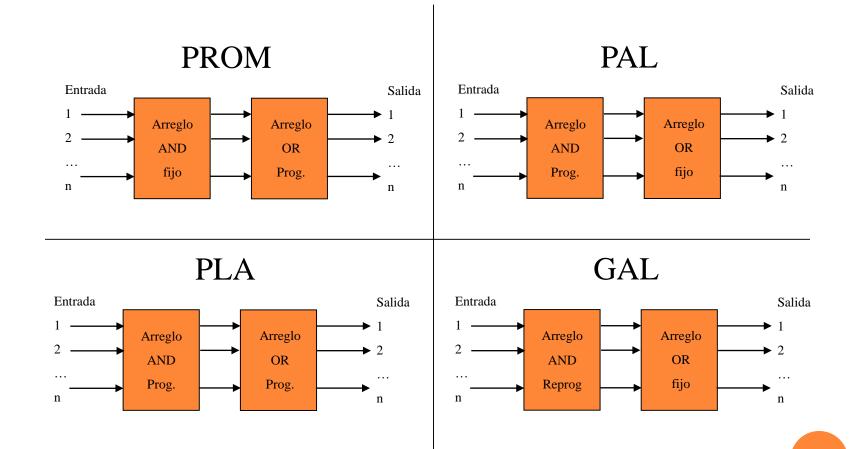

# CLASIFICACIÓN (ARQUITECTURA)

- PROM (Memoria programable de sólo lectura)

- PLA (Arreglo lógico programable)

- PAL (Lógica de arreglos programables)

- GAL (Arreglo lógico genérico)

- CPLD (Dispositivo lógico programable complejo)

- FPGA (Arreglos de compuertas programables mediante campos)

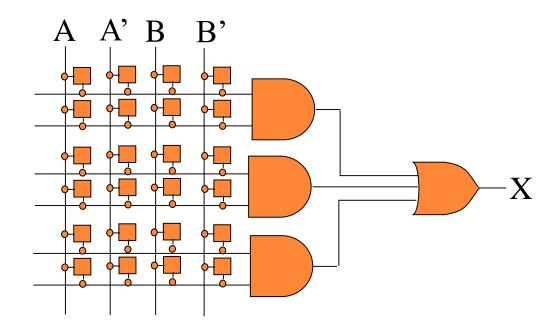

#### PLA

•Arreglo de compuertas:

Circuito con varias compuertas lógicas no conectadas.

Programable en función de la aplicación

#### PLA

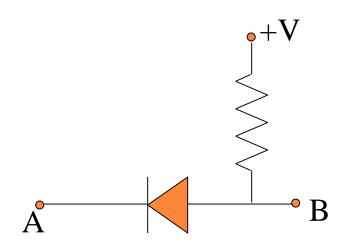

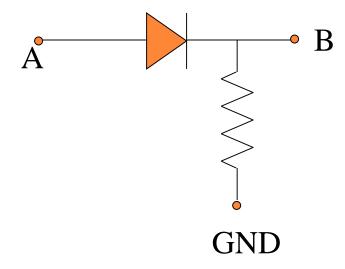

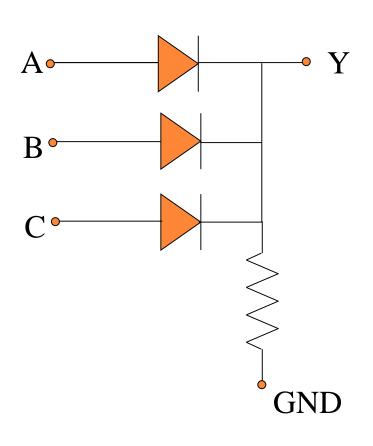

- Diodos en circuitos digitales:

- Funcionan como interruptor.

Resistencia Pull-up (Elevadora)

# PLA

Resistencia Pull-down (Reductora)

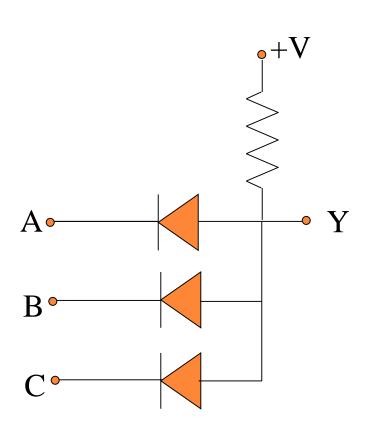

# COMPUERTA AND

| A | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

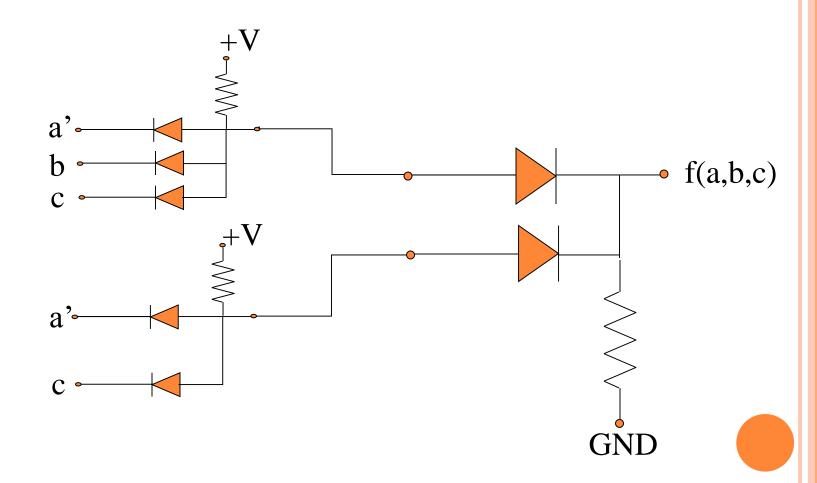

# COMPUERTA OR

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

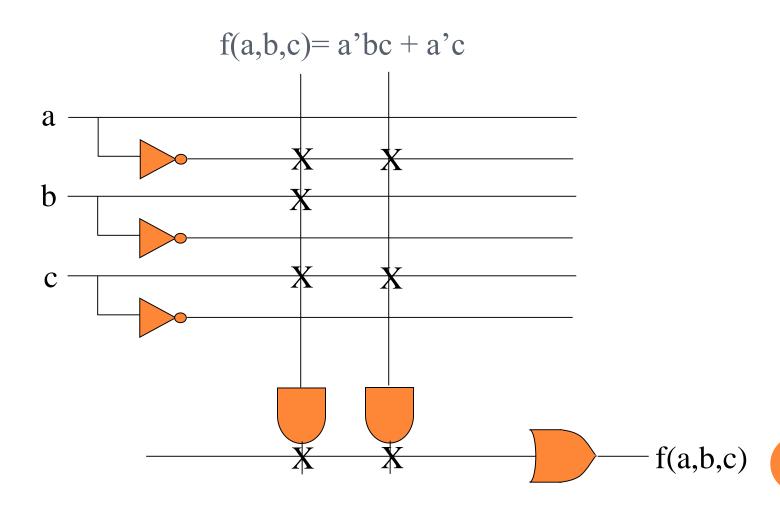

$$F(A,B,C) = A'BC + A'C$$

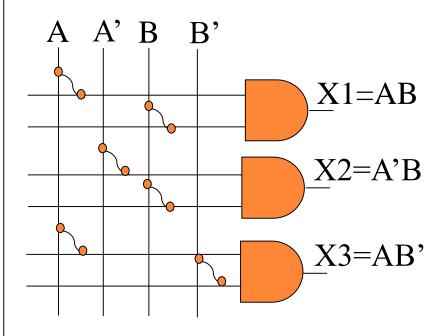

#### DIAGRAMA MATRICIAL

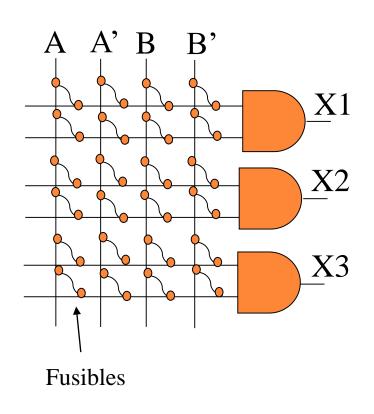

## ARREGLO PROGRAMABLE

# ESQUEMAS BÁSICOS DE DISPOSITIVOS

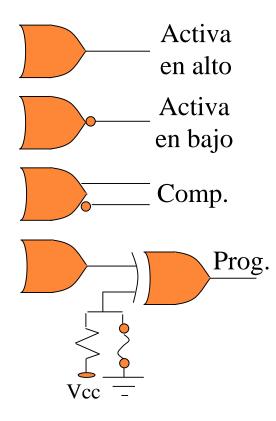

#### PROGRAMACIÓN GAL

Interruptor ON / OFF

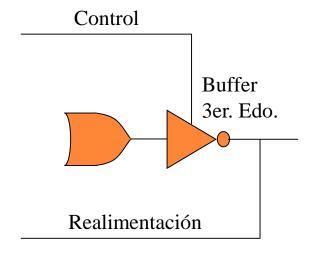

## SALIDAS

#### Realimentación

#### ARQUITECTURA

- o GAL 16V8

- o GAL 20V8

# Programación – Wincupl

| Operador | Ejemplo | Función |

|----------|---------|---------|

| !        | !A      | NOT     |

| &        | A&B     | AND     |

| #        | A#B     | OR      |

| \$       | A\$B    | XOR     |

# DISPOSITIVOS LÓGICOS PROGRAMABLES DE ALTO NIVEL DE INTEGRACIÓN

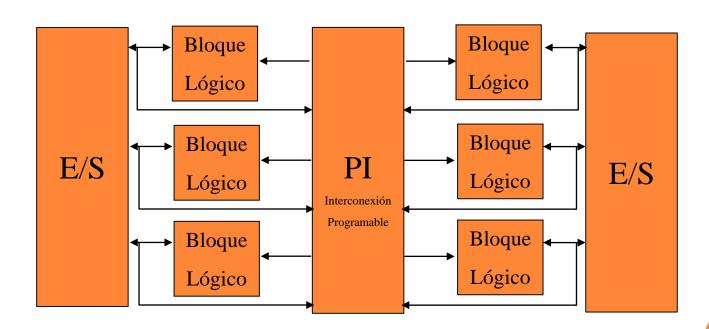

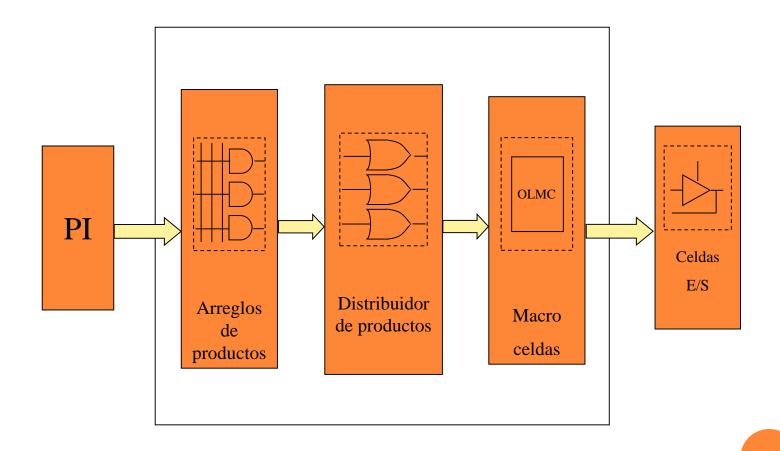

Dispositivos lógicos programables complejos (CPLD)

## BLOQUE LÓGICO PROGRAMABLE

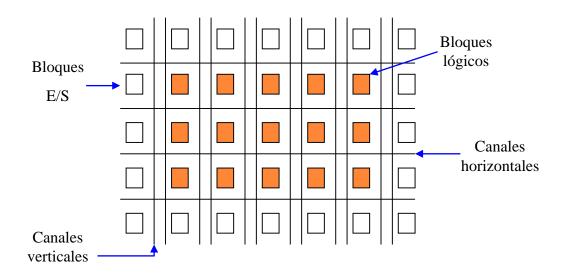

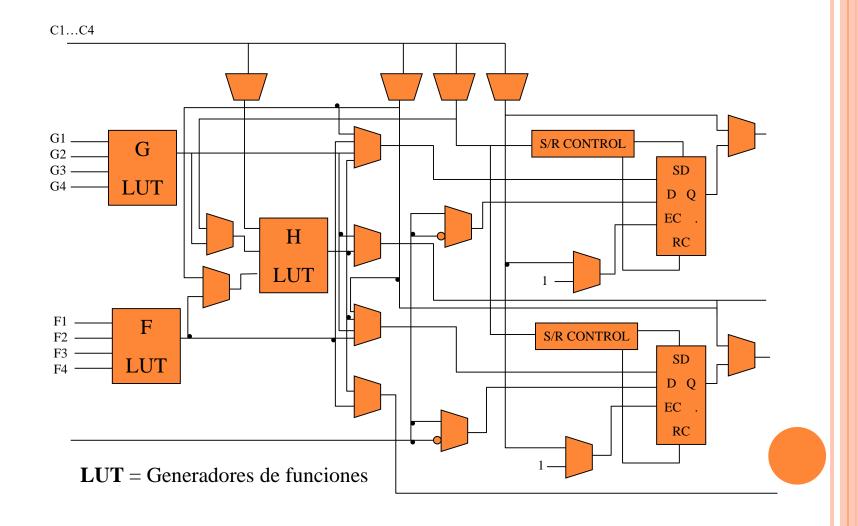

# ARREGLOS DE COMPUERTAS PROGRAMABLES POR CAMPOS (FPGA)

- Arreglos de compuertas

- Bloques lógicos configurables (CLB)

- Bloques de entrada salida (IOB)

- Canales de comunicación

#### BLOQUES LÓGICOS CONFIGURABLES

# DISPOSITIVOS

| Características | CPLD                                                         | FPGA                                                      |

|-----------------|--------------------------------------------------------------|-----------------------------------------------------------|

| Arquitectura    | Similar a un PLD  Más combinacional                          | Similar a arreglos de<br>compuertas<br>Mas registros +RAM |

| Densidad        | Baja a media                                                 | Media a alta                                              |

| Funcionalidad   | Frecuencias superiores a 200MHz                              | Depende de la<br>aplicación (+135<br>MHz)                 |

| Aplicaciones    | Contadores rápidos  Máquinas de estado  Lógica combinacional | Arquitectura de comp.  DSP  Diseños con registros         |

#### AMBIENTES DE DESARROLLO

## Compiladores

- PALASM (PAL Assembler)

- OPAL (Optimal PAL Languaje)

- PLPL (Programmable Logic Programming Languaje)

- ABEL (Advanced Boolean Expression Languaje)

- CUPL (Compiler Universal Programmable Logic)